# Design, Development, Testing and Demonstration of a 10-MVA, ETO-based StatCom

#### Phase 1

By: Dr. Harshad Mehta Founder and CEO

Funded in part by the Energy Storage Systems Program of the U.S. Department Of Energy through Sandia National Laboratories

November 4, 2010

## ETO-Based StatCom

# BACKGROUND Evolution of Project

- Department of Energy (DOE)

Energy Storage Program

- BPA

- North Carolina State University (NCSU) developed the <u>E</u>mitter <u>T</u>urn-Off Thyristor (ETO) and design for a Laboratory ready 10-MVA StatCom

- Silicon Power Corporation (SPCO) in FY2009 started to take Government supplied Designs and Equipment obtained from NCSU to work toward a practical and cost effective ETO-Based StatCom

# OBJECTIVE Purpose of Project

- Develop a 1.67MVA Full ETO-Based Bridge for Incorporation in a 10-MVA ETO-Based StatCom

- Field Test at BPA (Bonneville Power Administration) Lab

# TECHNICAL APPROACH

- ELECTRICAL

- **MECHANICAL**

- THERMAL

- **PACKAGING**

# ELECTRICAL STATUS

- Electrical Simulation

- **Boost Converter**

- H-Bridge

- Static Test

- **Boost Test**

- Low Power H-Bridge Test

- High Power H-Bridge Test (Limited)

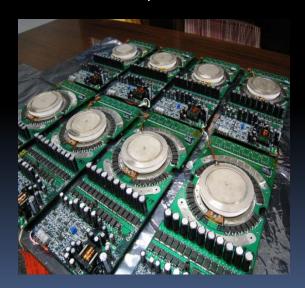

Static Test Fixture

**Boost Test Fixture**

H-Bridge Test Fixture

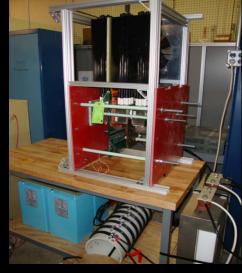

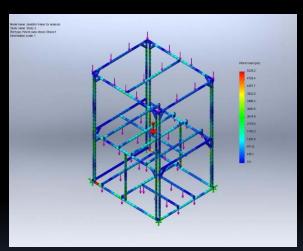

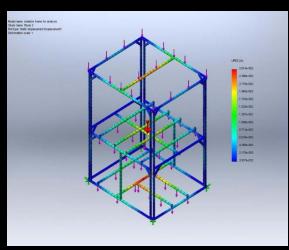

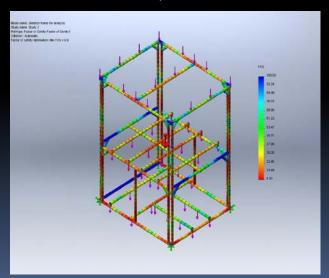

# MECHANICAL STATUS

Enclosure Stress Analysis Complete

Stress distribution across the framework

Resultant Displacement in the structural frame corresponding to loads

Factor of Safety for the frame

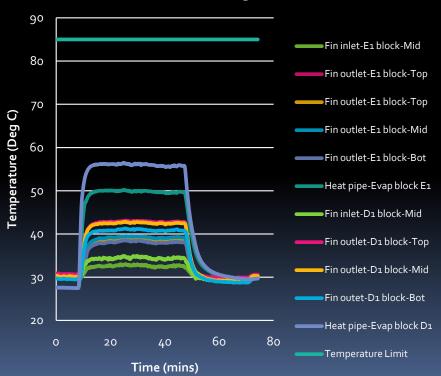

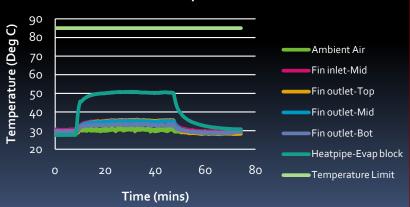

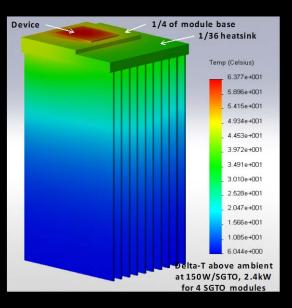

# THERMAL STATUS

- ETO-Based Half-Bridge

- Clamp /Snubber

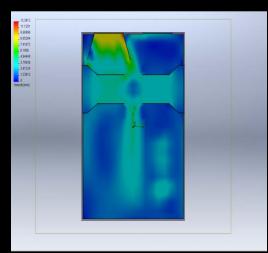

Thermal Response at High power (10.97 KW)

Plot for Half-bridge section

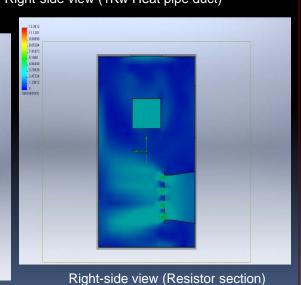

Thermal Response at High power (10.97 KW)

Plot for Clamp-circuit section

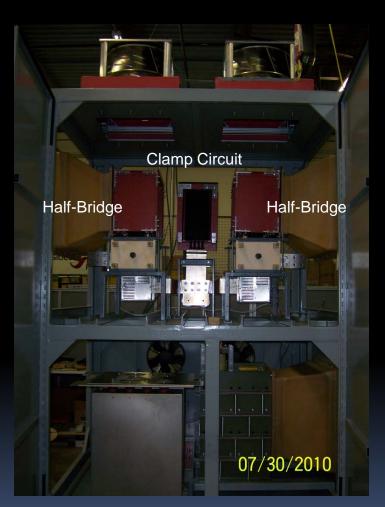

## PACKAGING STATUS

- Component Placement

- ETO-Based Half-Bridge

- Clamp Circuit

# TEST RESULTS

#### Static

- **4 ETO Modules Passed**

- 3 ETO Modules Failed

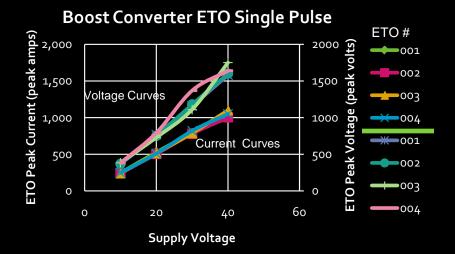

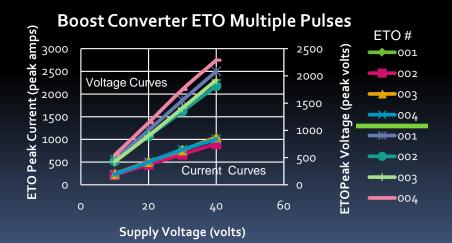

#### Boost

- 4 ETO Modules Passed (see graphs)

- 3 ETO Modules Failed

# TEST RESULTS (cont.)

- Thermal

- **Velocity Views**

Right-side view (1Kw Heat pipe duct)

Front view (2KW Heat pipe ducts)

Top view (Resistor section)

Top view

# TEST RESULTS (cont.)

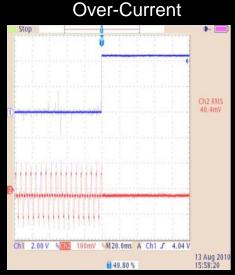

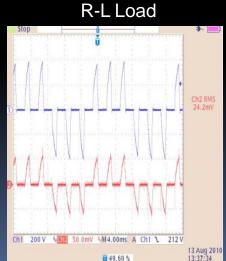

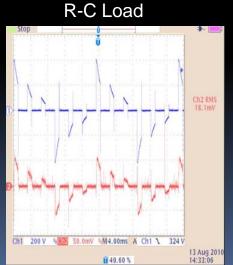

- ETO-Based H-Bridge Low Power

- 2 ETO Modules Needed Repair

- All 4 ETO Modules Demonstrated Soft-Switching

- Success in Driving ETO's in Various Modes:

- •Blue Traces Voltage Across Inductor

- •Red Traces

Current Across

Inductor

## ACCOMPLISHED

Mechanical Analysis and Simulation

**Electrical and Control Simulation**

Thermal Analysis and Simulation

Mechanical / Thermal Fabrication

Thermal Testing

ETO-Based H-Bridge Low Power Testing **Electrical Fabrication**

**Static Testing**

**Boost Testing**

Final Report Published and Cost Proposal for Phase 2 & 3 Submitted

## **NEXT STEPS**

## Hybrid Architecture

- Wafers Fabricated on a Standard IC Line

- Standard SPCO Die Size (12mm)

- Voltage and Current Sharing

- Thermal Management

- Air Cooled (No Liquids)

- Individual Control at Die Level

- Hybrid SGTO-ETO Function at Die Level

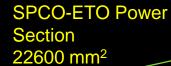

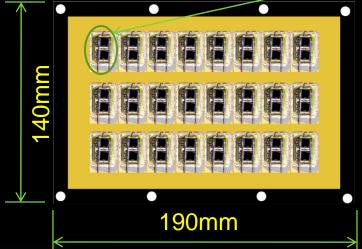

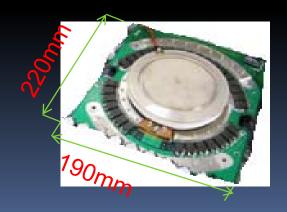

Std. ETO Power Section 41800mm<sup>2</sup> SPCO-ETO is

54% Area of Std.

ETO and 30% Less

Weight!

SILICON

POWER

# NEXT STEPS (cont.)

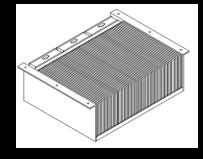

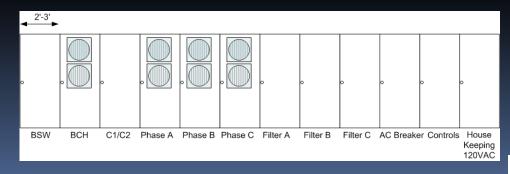

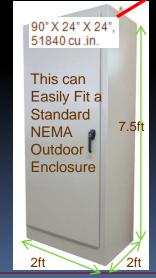

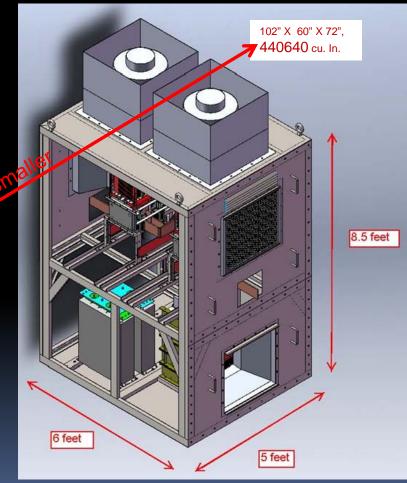

## System Architecture

- Standard Cabinet Size

- Modular Air Cooled

- Sectionalized by Function

- Serviceability

- Optional Redundancy

- Scalable

- Portable

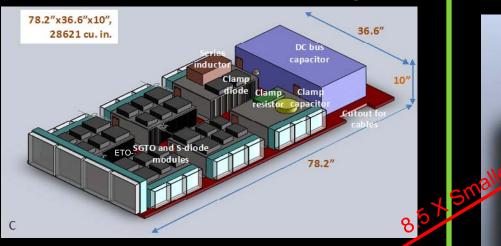

## **COMPARISON**

### NCSU-ETO-Based H-Bridge

# CONCLUSIONS/RECOMMENDATIONS

- Phase 1 Objectives Accomplished

- High Power Testing Limited by Devices

- Phase 2 Proposal Submitted to Develop a Commercially Feasible Product

- Vision: M (Manufacturable), U (Usable), S (Sellable), T (Technology)

## **ACKNOWLEDGEMENTS**

D.O.E. ENERGY PROGRAM for FUNDING

S.N.L. for TECHNICAL DIRECTION

**B.P.A. for the SYSTEM REQUIREMENTS**

**NC STATE UNIVERSITY**

N.C.S.U. ETO REQUIREMENTS