## **Scalable Smart Lighting Platform**

PARC, InnoSys, Inc, Wendy Davis Eugene Chow, Principal Scientist & Strategy Leader at PARC Phone: 650-812-4184, Email: echow@parc.com New Project: Agreement DE-EE0009693, BENEFIT2020

## **Project Summary**

#### A Smart Lighting Platform Goal

Save >50% building lighting energy. Dynamic, customized, directional light fields. Integrated, chip-based sensing and control. Thin, large area, flexible format

#### Key Barrier:

Fabrication cost. Need high chip count heterogeneous systems of millions of LEDs and other semiconductor chiplets.

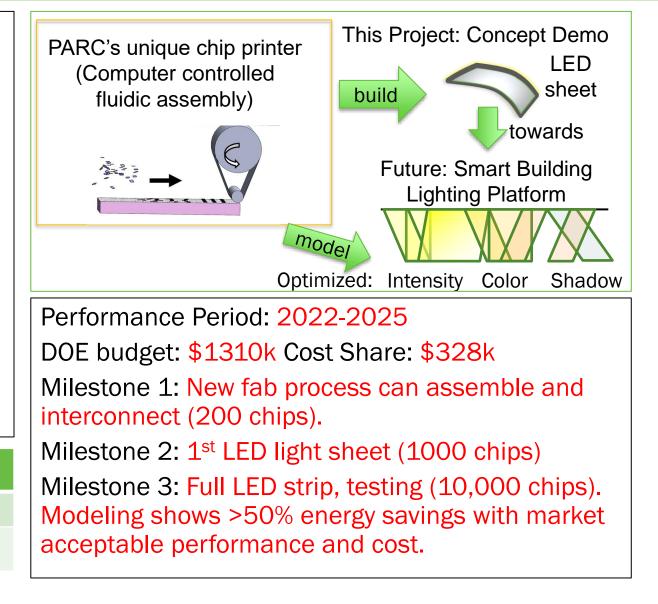

#### This project:

1) Model energy, performance cost tradeoffs.

2) De-risk cost by showing scalability of new chip printer process. Demo a thin flexible LED light sheet.

| PARC        | Project lead. Fab process, demo, modeling |  |  |  |

|-------------|-------------------------------------------|--|--|--|

| Innosys     | Support demo design, phosphor             |  |  |  |

| Wendy Davis | Advise modeling, market                   |  |  |  |

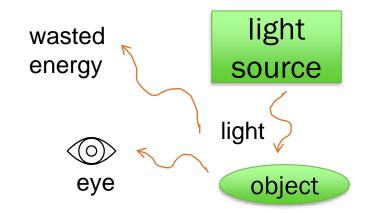

## **Problem – Light Application Efficiency (LAE) Unrealized**

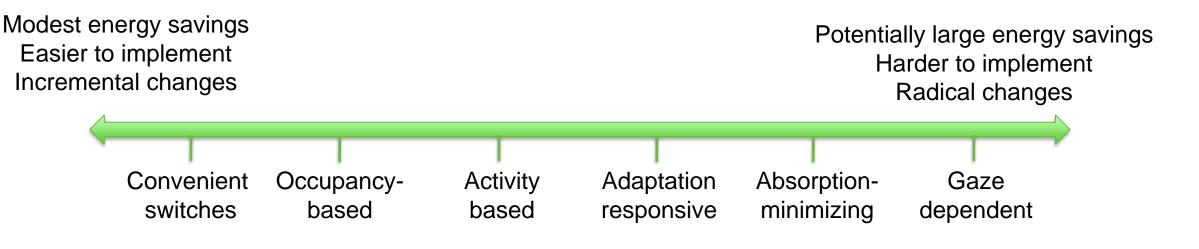

- Lighting consumes 18% of building electricity but most generated photons wasted as do not reach eyes

- 3x energy reduction gain possible through light application efficiency with smart directional/timed sources.<sup>1</sup> Gaze dependent most energy savings potential, but hardest to implement. Need new capability.

J.Y. Tsao, M.H. Crawford et al., Adv. Optical Mater. 2 (2014), 809.

## **Vision - New Smart Lighting Building Platform**

Future

Optimized light application efficiency New platform 50% less energy for office case

Current

## **Alignment and Impact**

#### Achieving Project Goals Enable Much Future Building Energy Savings

- Advance smart light sheet concept (LAE)

- Build 1st concept demonstrator

- 2-3x energy reduction possible for 18% of building electricity (lighting)

- More LED adoption by enabling attractive, thin, diffuse, flexible form factor

- >2 quads saved if remaining non-LED linear & low/high bay fixtures convert to LED

- >5 quads saved if rest of lighting markets also converts to LEDs

- Future cost reduction, mass adoption possible

- PARC printer 1000x lower cost potential than current approaches

#### **Success Definition**

- Show >50% energy savings, cost tradeoff

- Show scalable high chip count fab possible with basic LED light sheet demo.

#### **Broader DOE Impact Potential**

- <u>Smart building platform extendable to new</u> <u>functionality with heterogeneous IC chips</u>

- <u>Sensing people, environment...</u>

- PARC's microchip printer beyond lighting. High part count heterogeneous systems/materials.

- Semiconductor/photonics, computation, large area sensors (solar etc), microstructured materials, 2D materials, energetics...

## **Approach: Current Light Sources Limited**

No direction control+ low cost, currentmarket leader

- High glare

- Bulky

- Not diffuse

- + Directional

LumiCurve

- No direction control

- No sensors

- Poor robustness

- Poor customization

- Not tunable

- High cost

- + Diffuse, thin, flexible

#### LightPipe

- No direction control

- No sensors

- + Diffuse, thin, flexible

- + Low cost

## **Approach: Manufacturing Cost Key Barrier**

- Need millions of heterogeneous semiconductor microchips (per square meter) on thin flexible substrates

- $_{\odot}$  Current million chip systems >\$10<sup>5</sup>

- Assembly costs >>\$10<sup>4</sup> should reduce to ~\$1 for lighting market mass adoption

#### • Existing fabrication not scalable to low cost

- High chip count approaches are high cost & slow (robotic pick/place, laser, stamp)

- Other (non-PARC) fluidic assembly approaches have low-cost potential but low yield, not heterogenous.

- PARC's new chip printer process has low-cost scaling potential

- Designed for chip "ink"

- Xerographic printing \$1/m<sup>2</sup>

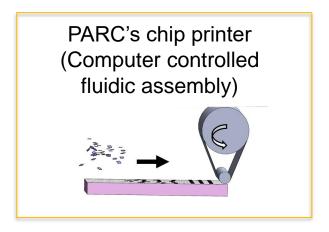

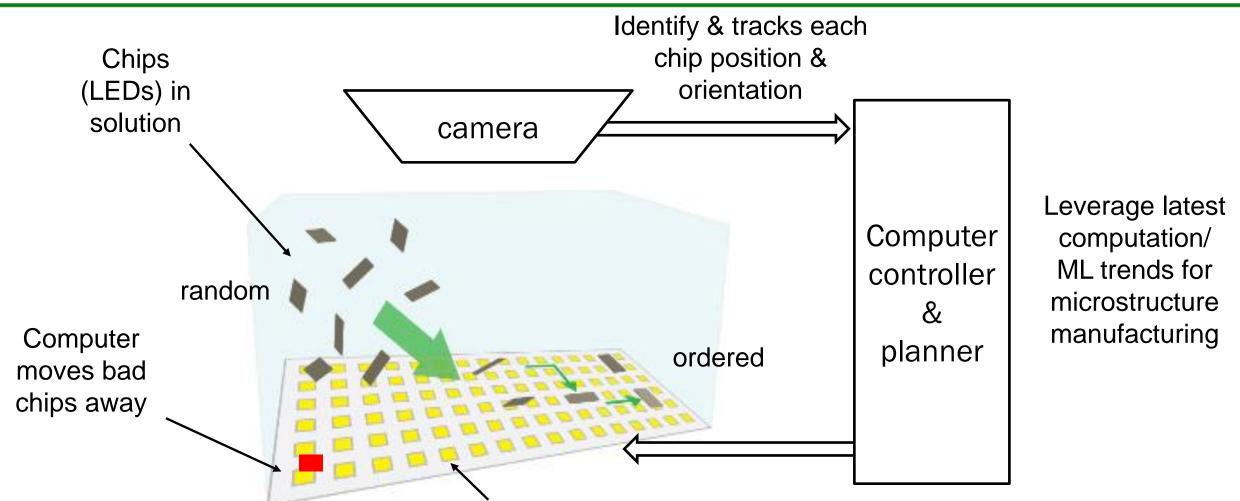

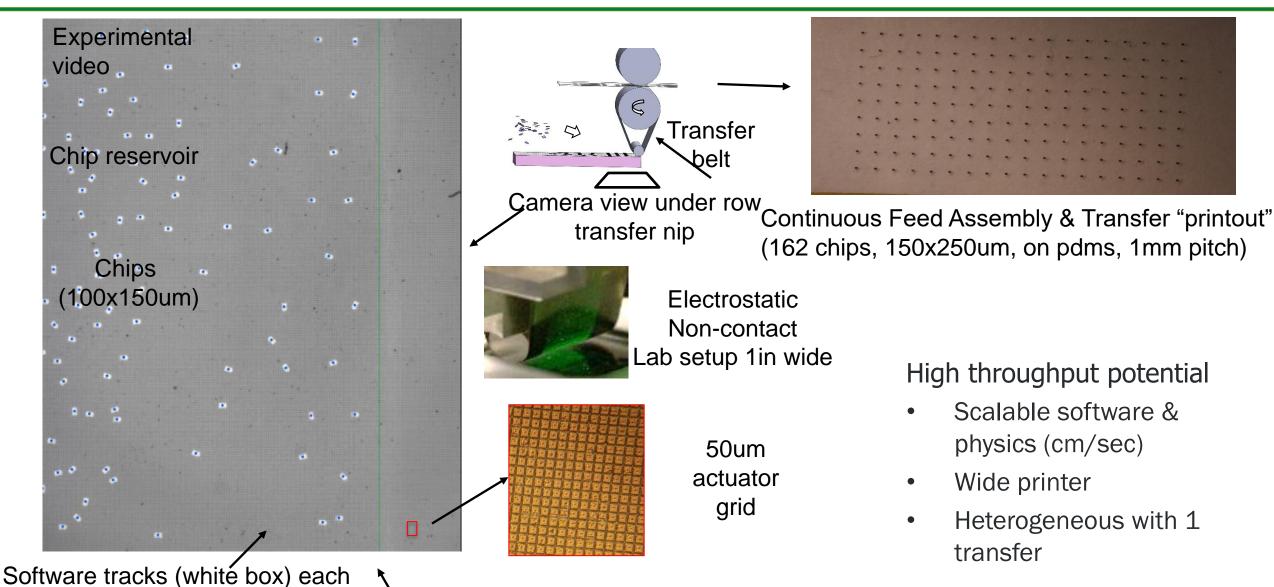

## New : Software directed electrostatic microassembly

Active matrix electrode array generates dynamic electric force fields to individually direct chips in parallel to target locations, enabling sorting, defect healing, heterogeneous.

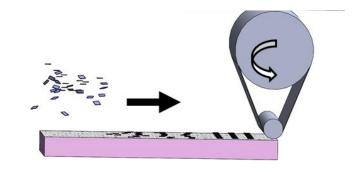

## **Computer Assembly Integrated With A Transfer Belt**

chip and moves chip to transfer U.S. DEPARTMENT OF ENERGY

Row transfer line

| # | Goal Type    | Goal                                                                                                          | Budget Period 1                        | Budget Period 2                     | Budget Period 3                               |  |  |

|---|--------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------|-----------------------------------------------|--|--|

| 1 | Experimental | Improve assembly printer<br>system to show scalability for<br>low cost. Demo thin, white light<br>LED sheet.  | 200 chips<br>(interconnect<br>process) | 1000 chips<br>(white light sheet)   | 10,000 chips<br>(full LED strip &<br>testing) |  |  |

| 2 | Modeling     | Show large energy savings of<br>new directional light sheet,<br>customizable platform, and cost<br>tradeoffs. | light output<br>model                  | energy savings for<br>key use cases | cost sensitivity<br>versus energy<br>savings  |  |  |

- Majority of resources planned for experimental goals (#1)

- Improve process to scale # of chips key challenge

- 100x more assembly and 1000x more interconnects than PARC's prior work

10

10

## **Approach: Challenges & Strategy**

- Challenges

- Low-cost with high chip count system and yield

- Mitigation: Prioritize yield understanding early

- Business strategy

- Build manufacturing tool, sell smart lighting sheet

- Engage investors/customers in lighting/display with modeling, demos

- Leverage LED display hot trends

- How will demonstrate benefit

- Modeling shows energy savings and cost tradeoffs

- Experiments show low-cost potential with new chip printer process.

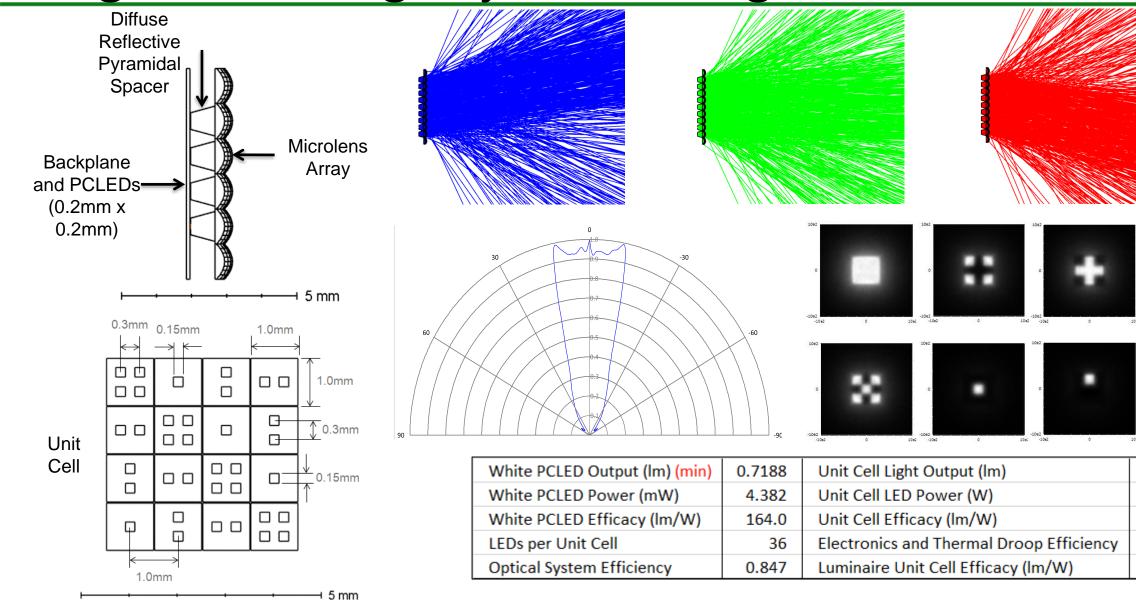

#### 12 Progress - Modeling a Dynamic LED Light Sheet

21.9

0.158

138.9

0.80

111.1

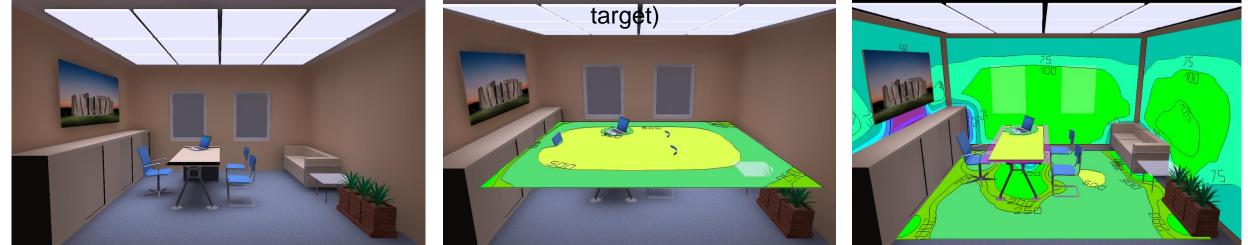

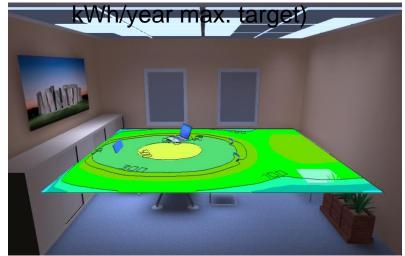

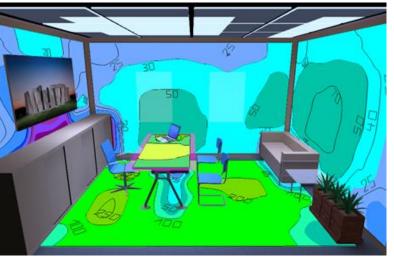

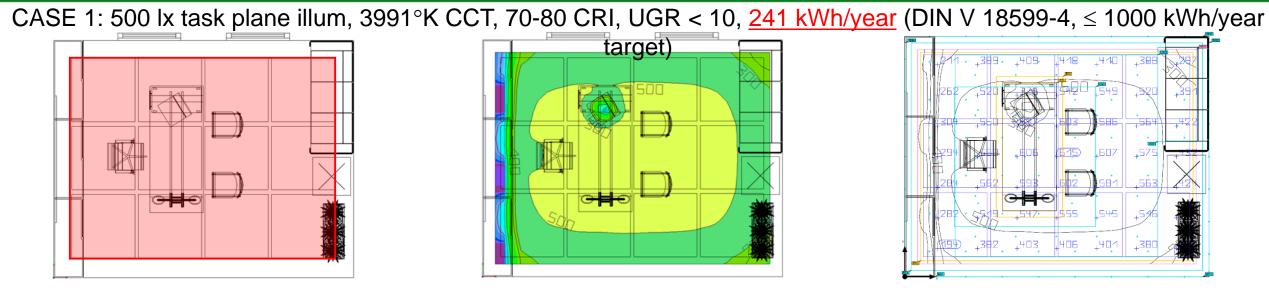

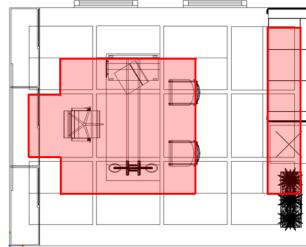

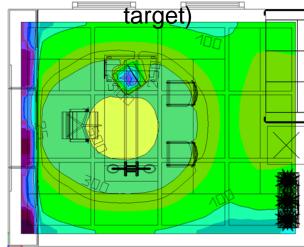

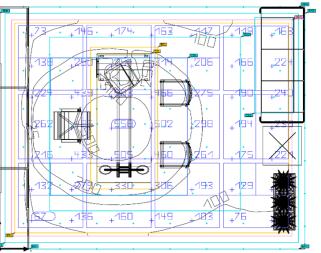

#### <sup>13</sup> Modeling Shows 50% Energy Savings for Office Example

CASE 1: 500 lx task plane illum, 3991°K CCT, 70-80 CRI, UGR < 10, 241 kWh/year (DIN V 18599-4, ≤ 1000 kWh/year

CASE 2: 500 lx task plane illuminance, 3991°K CCT, 70-80 CRI, UGR < 10, <u>122 kWh/year</u> (DIN V 18599-4, ≤ 1000

# <sup>14</sup> Comparison: 5m x 4m x 2.8m Basic Office Space Example

CASE 2: 500 lx task plane illum, 3991°K CCT, 70-80 CRI, UGR < 10, <u>122 kWh/year</u> (DIN V 18599-4, ≤ 1000 kWh/year

## **Progress and Future Work**

- 3 of 4 milestones for BP1 (of 3) achieved

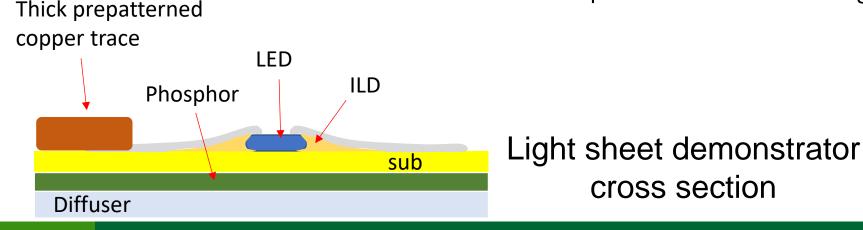

- Designed final demonstrator

- $_{\circ}$  Improved chip printer loading

- Modeled directional light sheet

- showed 50% energy savings, office case

- Unexpected Issues/Lessons

- $_{\circ}$   $\,$  NCE for support tool failure

- HW/SW system challenging

- Remaining Project Plans

- Build 1st electrically interconnect LED array, 1<sup>st</sup> white light sheet, final demonstrator.

- Increase # chips 100x, # interconnects 1000x over PARC's prior work.

- No new project changes anticipated

- Plans beyond end of the project

- $_{\odot}~$  Raise funds, mature tech, start company.

- Build production tool, high chip count product based on LED light sheets

# **THANK YOU**

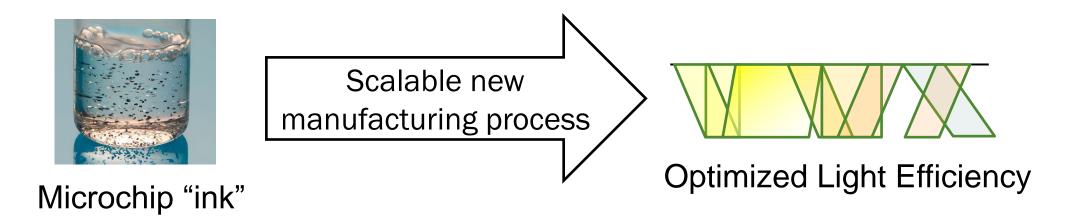

Scalable new manufacturing process Optimized Light Efficiency

Microchip "ink"

PARC, Innosys and Wendy Davis PI Eugene Chow, PhD, PARC Principal Scientist & Strategy Leader 650-812-4181, echow@parc.com New Project: Agreement DE-EE0009693, BENEFIT2020

## **REFERENCE SLIDES**

## **Project Execution**

|                                              | 21 | FY2022<br>292 |     | FY2023 |           |                           | FY2024<br>529 |           |    |       | FY2025<br>364<br>0        |                  |      |                         |    |    |         |

|----------------------------------------------|----|---------------|-----|--------|-----------|---------------------------|---------------|-----------|----|-------|---------------------------|------------------|------|-------------------------|----|----|---------|

| Planned budget (\$k)                         | 11 |               |     | 442    |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Spent budget (\$k)                           |    |               | 292 |        | 84        |                           |               | 0         |    |       |                           |                  |      |                         |    |    |         |

|                                              | Q4 | Q1            | Q2  | Q3     | Q4        | Q1                        | Q2            | Q3        | Q4 | Q1    | Q2                        | Q3               | Q4   | Q1                      | Q2 | Q3 | Q4      |

| Past Work Milestones                         |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q1 Design demonstrator                       |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q2 Loader                                    |    |               |     |        | $\bullet$ |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q4 Light output model                        |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Current/Future Work Milestones               |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q3 1st interconnect run                      |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q1 Interconnected LEDs                       |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q2 1st white light sheet                     |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q3 1000 chips interconnected                 |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q1 Full LED test strip                       |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q2 LED test strip testing                    |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| Q3 Improve yield                             |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

| NOF                                          |    |               |     |        |           |                           |               |           | -  | 4     |                           |                  |      |                         |    |    |         |

| NCE                                          |    |               |     |        | Go/No-Go: |                           |               | 200 chips |    |       |                           | 1000 chips 10,00 |      |                         |    |    |         |

| Did 1 <sup>st</sup> modeling milestone early |    | 90/N          |     |        |           | (1 <sup>st</sup> intercor |               |           |    | conne | onnects) (1 <sup>st</sup> |                  |      | light sheet) (final der |    |    |         |

|                                              |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    |    |         |

|                                              |    |               |     |        |           |                           |               |           |    |       |                           |                  |      |                         |    | P  | erforma |

|                                              |    |               |     |        |           |                           |               |           |    | •     | 🕨 pla                     | nned o           | date |                         |    |    | Cost M  |

| Who                 | Org Type                                                                                                      | Project Role                                                                                       |

|---------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| PARC                | 50 yr old industrial<br>research lab, 1 <sup>st</sup> laser<br>printer & 1 <sup>st</sup> personal<br>computer | Lead project, Improve chip printer process to<br>demonstrate 1st light sheet.<br>Perform modeling. |

| Innosys             | Small minority owned company                                                                                  | Support light sheet design, phosphor integration                                                   |

| Wendy<br>Davis      | Consultant, lighting application expert                                                                       | Guide modeling specs for market acceptance                                                         |

| Lumileds,<br>others | LED vendors                                                                                                   | Supply LEDs                                                                                        |

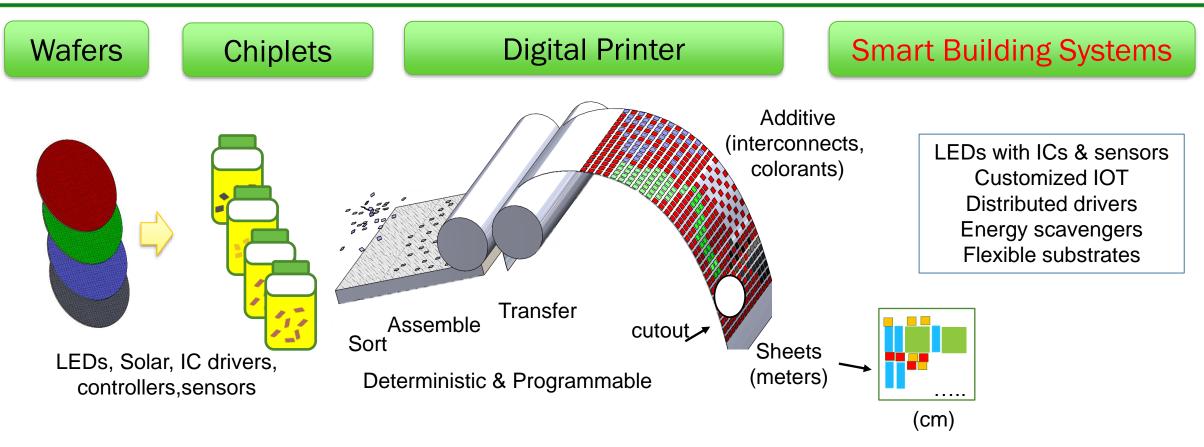

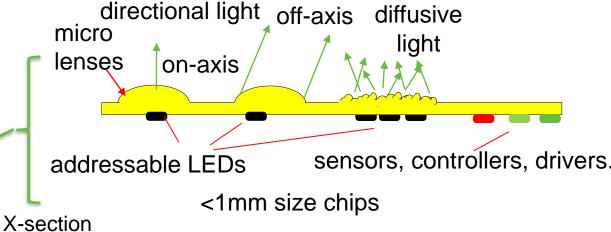

## **Vision: Microassembly Printer for Smart Systems**

- High throughput & low cost, heterogeneous of small chips (10-500um). Millions of chips.

- Digital sort chips, custom patterns, rapid prototyping

- Goal disruptive low cost of printing (\$2/m<sup>2</sup> for assembly & interconnect), *independent of number of devices*

- Smart Light Sheet Cost design, chips, substrates/optics & testing (assembly & interconnects negligible)

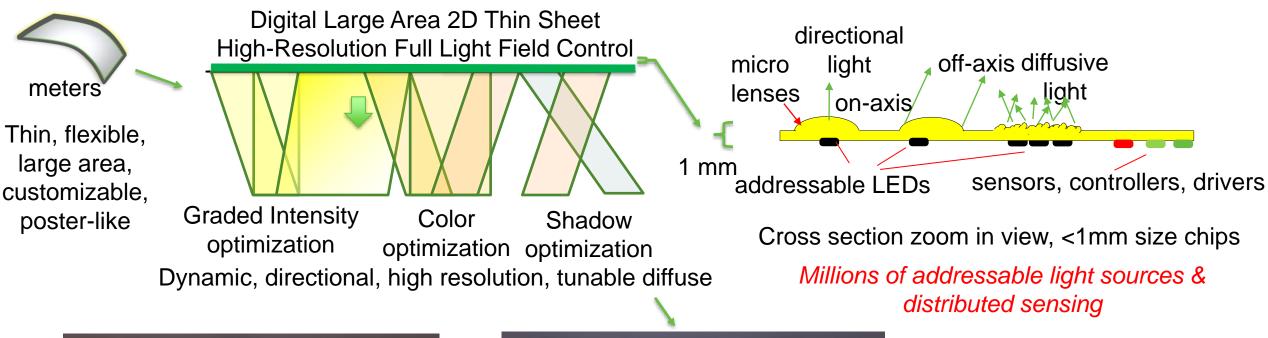

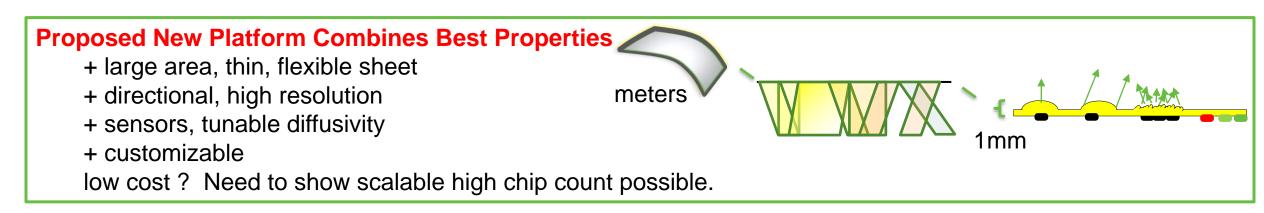

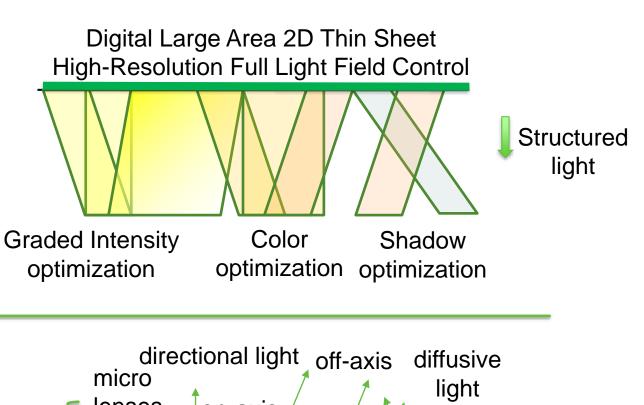

## Vision – A New Smart Building Lighting Platform Enabled by High Chip Count Systems

- Ideal source: light field generator

- Arrays of LEDs/lenses with programmable directional, fine scale control

- Diffuse, low glare desired for market adoption large area source

- Sensing, control, drivers..

- Thin, flexible adaptable form factor

- Customizable & Low cost

- Need high chip count system platform

- Millions of heterogeneous semiconductor chiplets on a flexible substrate. Current tools can't build.

- Need a new assembly integration manufacturing method

meters